基于數(shù)字集成電路技術(shù)的LCD數(shù)碼顯示器設(shè)計(jì)與實(shí)現(xiàn)

摘要:隨著信息顯示技術(shù)的飛速發(fā)展,LCD數(shù)碼顯示器因其功耗低、體積小、可靠性高等優(yōu)點(diǎn),在工業(yè)儀表、家用電器、便攜設(shè)備等領(lǐng)域得到了廣泛應(yīng)用。本文聚焦于采用數(shù)字集成電路技術(shù)進(jìn)行LCD數(shù)碼顯示器的核心設(shè)計(jì),詳細(xì)闡述了從系統(tǒng)架構(gòu)、數(shù)字邏輯設(shè)計(jì)到集成電路實(shí)現(xiàn)的全過程。

1. 引言

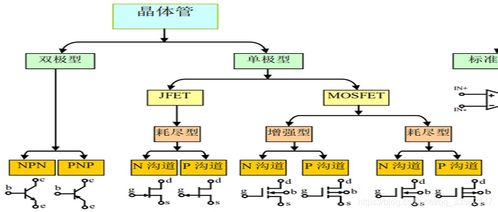

LCD數(shù)碼顯示器是一種利用液晶的電光效應(yīng)來顯示數(shù)字、字符或簡(jiǎn)單圖形的顯示器件。傳統(tǒng)的驅(qū)動(dòng)方式可能涉及分立元件或通用邏輯芯片,導(dǎo)致系統(tǒng)復(fù)雜、體積龐大。而基于專用數(shù)字集成電路(ASIC)或可編程邏輯器件(如CPLD、FPGA)的設(shè)計(jì),能夠?qū)⒖刂七壿嫛Ⅱ?qū)動(dòng)電路和時(shí)序生成高度集成,顯著提升系統(tǒng)的集成度、可靠性和性能。

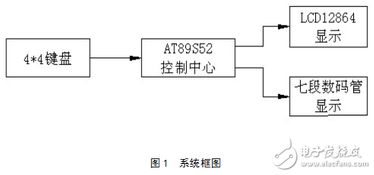

2. 系統(tǒng)總體架構(gòu)設(shè)計(jì)

一個(gè)典型的基于數(shù)字IC技術(shù)的LCD數(shù)碼顯示系統(tǒng)主要由以下幾部分構(gòu)成:

- 顯示數(shù)據(jù)接口模塊:負(fù)責(zé)接收來自微處理器或其它數(shù)字系統(tǒng)(如計(jì)數(shù)器、寄存器)的BCD碼或其它編碼的顯示數(shù)據(jù)。

- 控制與譯碼邏輯模塊:這是設(shè)計(jì)的核心。它將輸入的顯示數(shù)據(jù)(如4位BCD碼)轉(zhuǎn)換為對(duì)應(yīng)于LCD七段(或更多段,如帶小數(shù)點(diǎn)的八段)筆畫的段碼。生成LCD驅(qū)動(dòng)所需的交流波形控制信號(hào),以防止液晶直流極化損壞。

- 時(shí)序生成模塊:產(chǎn)生系統(tǒng)所需的工作時(shí)鐘,以及控制數(shù)據(jù)鎖存、刷新顯示的時(shí)序信號(hào)。

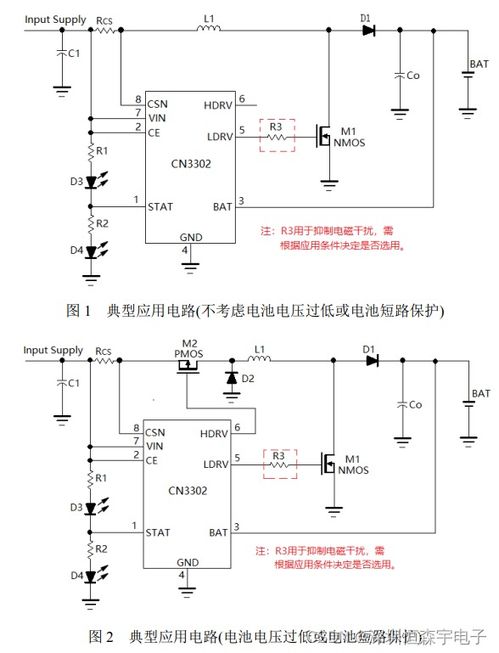

- 驅(qū)動(dòng)輸出模塊:將譯碼邏輯產(chǎn)生的低壓數(shù)字信號(hào),轉(zhuǎn)換為能夠驅(qū)動(dòng)液晶段點(diǎn)亮或熄滅的、具有一定電壓幅值的交流方波信號(hào)。

- 核心數(shù)字集成電路設(shè)計(jì)

- 譯碼器設(shè)計(jì):采用硬件描述語言(如Verilog HDL或VHDL)設(shè)計(jì)一個(gè)七段LCD譯碼器。該譯碼器的真值表需考慮LCD的驅(qū)動(dòng)特性:當(dāng)某段需要點(diǎn)亮?xí)r,其驅(qū)動(dòng)信號(hào)與背板(COM)信號(hào)應(yīng)為反相的交流方波;當(dāng)需要熄滅時(shí),則為同相的交流方波。因此,譯碼器輸出并非簡(jiǎn)單的‘1’或‘0’,而是代表相位狀態(tài)的邏輯值。

- 時(shí)序與控制邏輯設(shè)計(jì):設(shè)計(jì)一個(gè)狀態(tài)機(jī)或計(jì)數(shù)器,用于產(chǎn)生背板(COM)的交流方波(通常為占空比1:1的方波),并確保段驅(qū)動(dòng)信號(hào)(SEG)與之同步。關(guān)鍵是要確保驅(qū)動(dòng)電壓的直流分量為零。

- 多位數(shù)動(dòng)態(tài)掃描設(shè)計(jì):為了驅(qū)動(dòng)多位LCD數(shù)碼管并減少引腳數(shù)量,常采用動(dòng)態(tài)掃描(時(shí)分復(fù)用)技術(shù)。設(shè)計(jì)一個(gè)掃描計(jì)數(shù)器,循環(huán)選通每一位的公共端(COM),同時(shí)將對(duì)應(yīng)位的段碼數(shù)據(jù)同步送到段驅(qū)動(dòng)線上。這要求譯碼和驅(qū)動(dòng)模塊具備數(shù)據(jù)鎖存和快速切換能力。

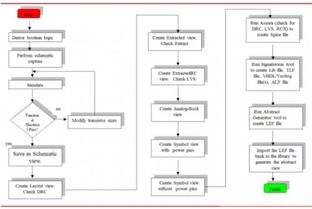

- 集成電路實(shí)現(xiàn)與驗(yàn)證

- 仿真驗(yàn)證:使用EDA工具(如ModelSim)對(duì)HDL代碼進(jìn)行功能仿真和時(shí)序仿真,驗(yàn)證譯碼正確性、交流驅(qū)動(dòng)波形以及動(dòng)態(tài)掃描邏輯。

- 綜合與實(shí)現(xiàn):將已驗(yàn)證的HDL代碼通過邏輯綜合工具,映射到目標(biāo)工藝庫(對(duì)于ASIC)或特定的FPGA/CPLD器件中。優(yōu)化面積和時(shí)序。

- 物理設(shè)計(jì)與輸出:對(duì)于ASIC設(shè)計(jì),需要進(jìn)行布局布線、版圖設(shè)計(jì)、設(shè)計(jì)規(guī)則檢查(DRC)和電路規(guī)則檢查(LVS)。最終生成用于芯片制造的GDSII文件。對(duì)于FPGA,則生成配置文件。

- 測(cè)試:制作測(cè)試電路板,將編程后的FPGA或制成的ASIC芯片與LCD面板連接,進(jìn)行實(shí)際顯示測(cè)試,驗(yàn)證其功能與可靠性。

- 優(yōu)勢(shì)與挑戰(zhàn)

- 優(yōu)勢(shì):高度集成化,系統(tǒng)體積小,功耗低;設(shè)計(jì)靈活,可通過修改HDL代碼快速適配不同顯示內(nèi)容或LCD型號(hào);性能穩(wěn)定,抗干擾能力強(qiáng);便于批量生產(chǎn),成本可控。

- 挑戰(zhàn):需要精確的時(shí)序設(shè)計(jì)以確保LCD的交流驅(qū)動(dòng)和動(dòng)態(tài)掃描無閃爍;對(duì)驅(qū)動(dòng)電壓的精度和對(duì)稱性有要求;在高位數(shù)或多路復(fù)用情況下,需平衡掃描頻率與顯示亮度的關(guān)系。

6. 結(jié)論

基于數(shù)字集成電路技術(shù)設(shè)計(jì)LCD數(shù)碼顯示器,是現(xiàn)代電子系統(tǒng)小型化、智能化的必然選擇。通過自頂向下的設(shè)計(jì)方法,利用硬件描述語言和先進(jìn)的EDA工具,可以高效、可靠地完成從邏輯設(shè)計(jì)到物理實(shí)現(xiàn)的全過程。這種設(shè)計(jì)不僅提升了產(chǎn)品性能,也為實(shí)現(xiàn)更復(fù)雜的顯示控制(如字符點(diǎn)陣LCD驅(qū)動(dòng))奠定了堅(jiān)實(shí)的技術(shù)基礎(chǔ)。隨著低功耗芯片技術(shù)和更先進(jìn)顯示技術(shù)的融合,此類集成化顯示解決方案將擁有更廣闊的應(yīng)用前景。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.chao321.cn/product/57.html

更新時(shí)間:2026-01-07 06:30:35