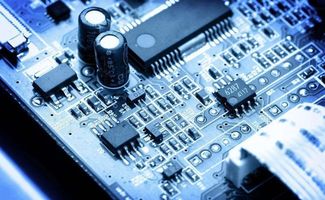

集成電路設(shè)計(jì) 數(shù)字時(shí)代的基石

集成電路設(shè)計(jì)是現(xiàn)代電子工業(yè)的核心技術(shù)之一,它涉及將數(shù)百萬甚至數(shù)十億的電子元件集成到微小的芯片上。隨著信息技術(shù)的飛速發(fā)展,集成電路設(shè)計(jì)已成為推動(dòng)科技進(jìn)步的關(guān)鍵力量。

集成電路設(shè)計(jì)的過程通常包括系統(tǒng)架構(gòu)設(shè)計(jì)、邏輯設(shè)計(jì)、電路設(shè)計(jì)和物理設(shè)計(jì)等多個(gè)階段。設(shè)計(jì)人員首先根據(jù)功能需求確定芯片的整體架構(gòu),然后利用硬件描述語言(如Verilog或VHDL)進(jìn)行邏輯設(shè)計(jì),將功能轉(zhuǎn)化為具體的電路結(jié)構(gòu)。接下來是電路設(shè)計(jì)階段,工程師需要優(yōu)化晶體管的布局和連接,以確保性能、功耗和面積的平衡。物理設(shè)計(jì)階段將電路圖轉(zhuǎn)化為實(shí)際的版圖,并通過仿真和驗(yàn)證確保設(shè)計(jì)的正確性。

在集成電路設(shè)計(jì)中,EDA(電子設(shè)計(jì)自動(dòng)化)工具扮演著不可或缺的角色。這些工具能夠幫助設(shè)計(jì)人員高效完成布局布線、時(shí)序分析和功耗優(yōu)化等復(fù)雜任務(wù)。隨著工藝節(jié)點(diǎn)的不斷縮小,設(shè)計(jì)人員還面臨著信號完整性、熱管理和制造變異等挑戰(zhàn)。

未來,集成電路設(shè)計(jì)將繼續(xù)向更高集成度、更低功耗和更強(qiáng)功能的方向發(fā)展。人工智能、物聯(lián)網(wǎng)和5G等新興技術(shù)的興起,對芯片設(shè)計(jì)提出了更高的要求。只有不斷創(chuàng)新和優(yōu)化設(shè)計(jì)方法,才能滿足日益增長的市場需求,為數(shù)字社會(huì)奠定堅(jiān)實(shí)的基礎(chǔ)。

如若轉(zhuǎn)載,請注明出處:http://www.chao321.cn/product/27.html

更新時(shí)間:2026-01-07 22:55:29