CMOS射頻集成電路設(shè)計 原理、挑戰(zhàn)與應(yīng)用前景

隨著無線通信技術(shù)的飛速發(fā)展,CMOS射頻集成電路(RFIC)設(shè)計已成為現(xiàn)代電子系統(tǒng)不可或缺的核心技術(shù)。本文將系統(tǒng)介紹CMOS射頻集成電路設(shè)計的基本原理、關(guān)鍵技術(shù)挑戰(zhàn)及其在多個領(lǐng)域的應(yīng)用前景。

一、CMOS射頻集成電路設(shè)計的基礎(chǔ)原理

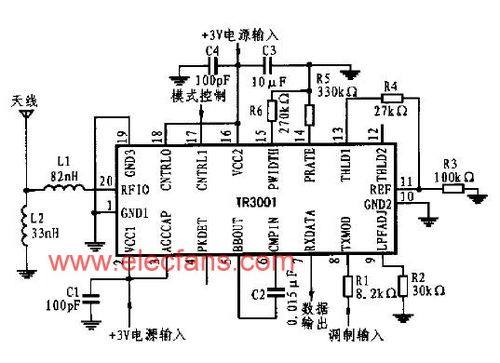

CMOS射頻集成電路設(shè)計主要涉及高頻信號的產(chǎn)生、調(diào)制、放大和接收等關(guān)鍵功能。與傳統(tǒng)的數(shù)字CMOS電路不同,射頻電路需在高頻環(huán)境下工作,通常范圍從幾百MHz到幾十GHz。設(shè)計過程中需要考慮寄生參數(shù)、阻抗匹配、噪聲系數(shù)和非線性失真等關(guān)鍵因素。CMOS工藝的優(yōu)勢在于其低成本、高集成度和良好的可擴展性,但同時也面臨著襯底損耗、低品質(zhì)因數(shù)被動元件等固有局限。

二、關(guān)鍵技術(shù)挑戰(zhàn)與解決方案

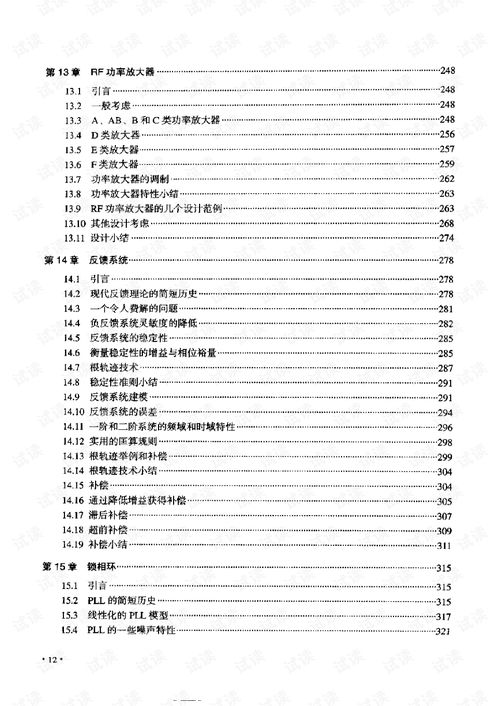

- 噪聲優(yōu)化:射頻接收機的靈敏度直接受限于電路噪聲。設(shè)計師需通過低噪聲放大器(LNA)拓撲優(yōu)化和阻抗匹配技術(shù)來最小化噪聲系數(shù)。

- 線性度提升:功率放大器(PA)和混頻器等模塊易受非線性失真影響。采用前饋、預(yù)失真等線性化技術(shù)可顯著改善系統(tǒng)性能。

- 功耗與效率平衡:移動設(shè)備對功耗極為敏感。通過 envelope tracking、平均功率跟蹤等動態(tài)偏置技術(shù),可在保證性能的同時優(yōu)化能效。

- 系統(tǒng)集成:將射頻前端、模擬基帶和數(shù)字處理電路集成在單一芯片上面臨著襯底耦合、電源噪聲等挑戰(zhàn)。采用深溝槽隔離、多電源域設(shè)計等方法可有效緩解這些問題。

三、典型應(yīng)用場景與發(fā)展趨勢

CMOS射頻集成電路已廣泛應(yīng)用于:

- 5G/6G通信系統(tǒng):實現(xiàn)毫米波頻段的大規(guī)模MIMO和波束成形

- 物聯(lián)網(wǎng)設(shè)備:為低功耗廣域網(wǎng)絡(luò)提供高能效的收發(fā)器

- 汽車雷達:支持77GHz頻段的自動駕駛感知系統(tǒng)

- 醫(yī)療電子:用于可穿戴設(shè)備的生物信號無線傳輸

未來發(fā)展趨勢包括:

- 異質(zhì)集成:將CMOS與III-V族化合物半導體結(jié)合,突破性能瓶頸

- 人工智能輔助設(shè)計:利用機器學習算法加速設(shè)計優(yōu)化過程

- 太赫茲電路探索:向更高頻段拓展以支持下一代通信需求

CMOS射頻集成電路設(shè)計作為連接數(shù)字世界與無線通信的橋梁,其技術(shù)突破將持續(xù)推動整個電子信息產(chǎn)業(yè)的創(chuàng)新發(fā)展。隨著工藝節(jié)點的不斷進步和設(shè)計方法的日益成熟,CMOS射頻集成電路必將在更多領(lǐng)域展現(xiàn)其重要價值。

如若轉(zhuǎn)載,請注明出處:http://www.chao321.cn/product/1.html

更新時間:2026-01-07 23:10:59