集成電路設(shè)計(jì)開源EDA工具合集 助力芯片開發(fā)的免費(fèi)與靈活解決方案

隨著集成電路(IC)設(shè)計(jì)變得越來越復(fù)雜,電子設(shè)計(jì)自動(dòng)化(EDA)工具在芯片開發(fā)中扮演著關(guān)鍵角色。傳統(tǒng)商業(yè)EDA工具雖然功能強(qiáng)大,但往往價(jià)格昂貴,限制了中小企業(yè)和個(gè)人開發(fā)者的參與。開源EDA工具的出現(xiàn)打破了這一局面,提供了免費(fèi)、靈活且可定制化的解決方案。本文將介紹一個(gè)完整的開源EDA工具合集,涵蓋集成電路設(shè)計(jì)的各個(gè)階段,包括電路設(shè)計(jì)、仿真、布局與驗(yàn)證等。

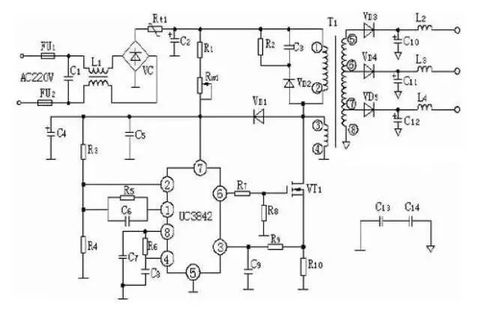

一、電路設(shè)計(jì)與仿真工具

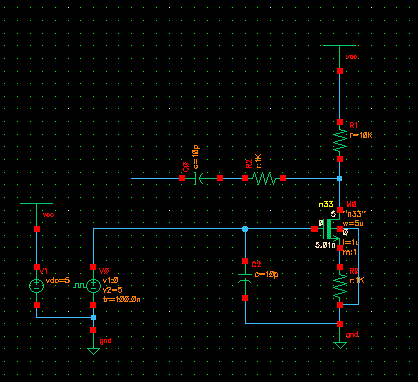

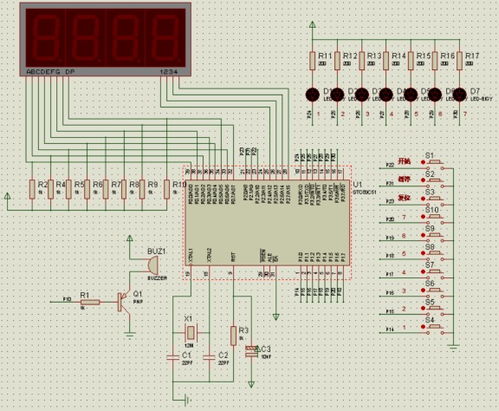

- KiCad:一款功能強(qiáng)大的開源電子設(shè)計(jì)自動(dòng)化套件,支持原理圖設(shè)計(jì)和PCB布局,適用于數(shù)字和模擬電路設(shè)計(jì)。其內(nèi)置的仿真工具可幫助用戶進(jìn)行電路性能測(cè)試。

- Ngspice:基于SPICE的開源電路仿真器,支持模擬和混合信號(hào)仿真,是驗(yàn)證集成電路設(shè)計(jì)功能的重要工具。

- GHDL:針對(duì)VHDL語言的開源仿真器,適用于數(shù)字電路設(shè)計(jì),支持IEEE標(biāo)準(zhǔn),兼容多種操作系統(tǒng)。

二、布局與物理設(shè)計(jì)工具

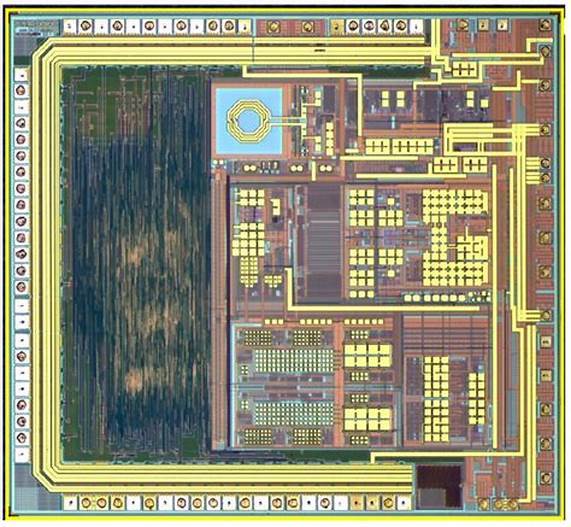

- Magic:一款歷史悠久的開源VLSI布局工具,特別適用于定制集成電路設(shè)計(jì),提供交互式布局編輯和設(shè)計(jì)規(guī)則檢查(DRC)功能。

- OpenROAD:由DARPA支持的開源項(xiàng)目,旨在實(shí)現(xiàn)“無人干預(yù)”的芯片設(shè)計(jì)流程,包括自動(dòng)布局與布線(P&R)、時(shí)序優(yōu)化等。

- KLayout:主要用于版圖設(shè)計(jì)和查看,支持GDSII和OASIS格式,提供強(qiáng)大的腳本擴(kuò)展功能。

三、綜合與驗(yàn)證工具

- Yosys:一款流行的開源邏輯綜合工具,支持Verilog和SystemVerilog,可將高級(jí)硬件描述語言轉(zhuǎn)換為門級(jí)網(wǎng)表。

- Icarus Verilog:輕量級(jí)的Verilog仿真工具,適用于小型到中型數(shù)字電路設(shè)計(jì)的驗(yàn)證。

- SymbiYosys:基于Yosys的形式驗(yàn)證工具,用于檢查設(shè)計(jì)是否符合規(guī)范,尤其適用于安全關(guān)鍵應(yīng)用。

四、生態(tài)系統(tǒng)與社區(qū)支持

開源EDA工具不僅免費(fèi),還受益于活躍的社區(qū)貢獻(xiàn)。例如,Qucs(Quite Universal Circuit Simulator)提供了圖形化界面,適合初學(xué)者;而OpenLANE項(xiàng)目則整合了多個(gè)工具,形成完整的RTL-to-GDSII流程。像LibreSilicon這樣的項(xiàng)目致力于開源半導(dǎo)體制造,進(jìn)一步降低了芯片開發(fā)的門檻。

五、優(yōu)勢(shì)與挑戰(zhàn)

開源EDA工具的優(yōu)勢(shì)在于成本低、透明度高和可定制性。用戶可以根據(jù)需求修改源代碼,適應(yīng)特定項(xiàng)目。與商業(yè)工具相比,開源工具可能在性能、支持和技術(shù)文檔方面存在不足。因此,用戶需要權(quán)衡利弊,選擇適合自身需求的工具鏈。

開源EDA工具為集成電路設(shè)計(jì)提供了可行的替代方案,尤其適合教育、研究和初創(chuàng)企業(yè)。隨著社區(qū)的不斷壯大,這些工具的功能和穩(wěn)定性將持續(xù)提升,推動(dòng)芯片設(shè)計(jì)的民主化進(jìn)程。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.chao321.cn/product/8.html

更新時(shí)間:2026-01-07 09:26:00